高密度・低コストの組み込み系メモリ技術「Z-RAM」

スイスのInnovative Siliconは、SOC(システム・オン・チップ)用の組み込み系DRAMメモリ技術「Z-RAM」を発表した。標準的なロジック・プロセスで高密度・低コストを実現するのが特徴で、特別な材料やマスク・ステップ増が必要ないという。今後、PCやPC周辺機器、コンシューマエレクトロニクス分野での市場参入を目指す。

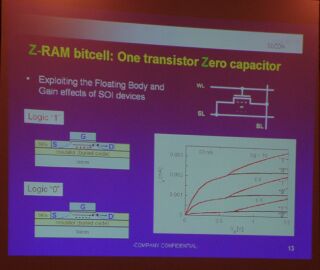

Z-RAMは、基本的にはSOI(シリコン・オン・インシュレータ)技術を採用したもの。SOIとは、絶縁膜(インシュレータ)上に形成した単結晶シリコンを基板(シリコンウエハー)とした半導体技術を指す。これにより電荷を貯めるためのキャパシタ(コンデンサ)を利用せずにすむ「ゼロキャパシタ」を実現しており、単一トランジスタのみでセルを構成できる。なお、Z-RAMの“Z”は“ゼロ(Zero)キャパシタ”のZだという。

SOIデバイスには、デバイス本体に過剰電荷が発生する「フローティング・ボディ効果」が存在する。同社では、「“好ましくない現象”とされているこの効果をコントロールし、強化することで『1』『0』のロジックを分ける」ことに成功した。これにより、メモリとして1/0のバイナリ情報を扱えるという。なお、情報の読み出しには電流センスアンプを用いて、選択したセルの電流と基準セルの電流を比較する仕組み。

高密度、低コスト、低電圧

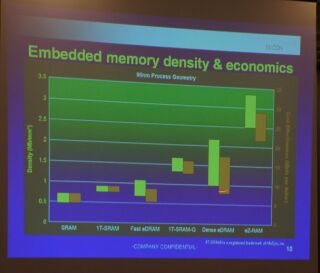

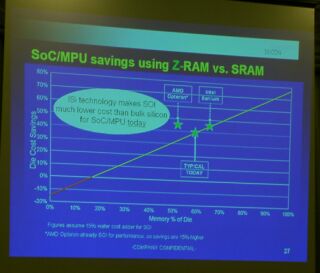

Z-RAMではダイ面積を、同じプロセス技術を用いた従来のDRAMやSRAMと比較して「半分から5分の1にすることが可能」(同社)。その分、コストを下げられるという。

SOIウエハーを利用する分、初期投資はやや高くなるが、チップ上のメモリ占有率が高くなれば従来のシリコンウェアよりはるかに低コストにできるとうたう。

低消費電力も特徴だ。SOI技術を標榜する企業はほかにもあるが、「ほかが低消費電力を実現しているとは思わない」(同社)。具体的には、従来のシリコンウェアと比較して消費電力を35%低減している。書き込み時にトランジスタをオフにするなどして、こうした低消費電力を実現しているという。

IPで提供予定、コンシューママーケット目指す

同社はZ-RAMをIPライセンスとして供与するかたちを考えている。ライセンスモデルとしては、自らメモリを設計・変更できる「技術ライセンス」や、メモリ・コンパイラを用いてインスタンスを生成できる「コンパイラ・ライセンス」など、各種方式を用意するという。

現在は、メガビット・サイズを実現し3ナノ秒の読み書き速度を持つテストチップを、90ナノプロセスで製作中。ビットセル・サイズは0.18マイクロメートルとなっている。「今後さらに22ナノのデザインルールにスケールダウンすることも可能」。

参入可能なマーケットとしては、ネットワーク機器、PC周辺機器などのSOCへの埋め込みを想定する。日本はコンシューマデバイスの市場が大きく、Z-RAMの技術が導入される余地はあると見ており、「米国よりも日本でいち早く発表したのは、そのためだ」とした。

関連記事

- 「積極的な半導体設備投資は“PS2のおかげ”」――ソニー、2000億円投資で次世代チップ「CELL」製造へ

ソニーとSCEIが総額約2000億円の設備投資を発表。次世代プロセッサ「CELL」の生産を目指した今回の巨額設備投資は、ソニーグループが掲げるブロードバンド戦略にとって重要な位置付けとなる - ソニーらが自信を持つCellの差別化要素とは

IBM、東芝、ソニーグループは差別化要素として、CellがWindowsやUNIX、Linuxなど多様なOSや家電・ゲーム機用のリアルタイムOSの実行をサポートする点を挙げている。 - IBM、消費電力大幅削減の携帯電話用半導体技術

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 楽天モバイルのスマホが乗っ取られる事案 同社が回線停止や楽天ID/パスワード変更などを呼びかけ (2024年04月23日)

- シャープ、5月8日にスマートフォンAQUOSの新製品を発表 (2024年04月24日)

- スマホを携帯キャリアで買うのは損? 本体のみをお得に買う方法を解説 (2024年04月24日)

- Vポイントの疑問に回答 Tポイントが使えなくなる? ID連携をしないとどうなる? (2024年04月23日)

- 通信品質で楽天モバイルの評価が急上昇 Opensignalのネットワーク体感調査で最多タイの1位 (2024年04月25日)

- スマートグラス「Rokid Max 2」発表 補正レンズなくても視度調節可能 タッチ操作のリモコン「Rokid Station 2」も (2024年04月25日)

- Apple、5月7日に新型iPad発表か イベント表題は「何でもあり」、Apple Pencilのイラストも (2024年04月24日)

- ドコモ、「Xperia 10 V」を5万8850円に値下げ 「iPhone 15(128GB)」の4.4万円割引が復活 (2024年04月25日)

- 中古スマホが突然使えなくなる事象を解消できる? 総務省が「ネットワーク利用制限」を原則禁止する方向で調整 (2024年04月25日)

- 「iPhone 15」シリーズの価格まとめ【2024年4月最新版】 ソフトバンクのiPhone 15(128GB)が“実質12円”、一括は楽天モバイルが最安 (2024年04月05日)

Innovative Siliconのマーク・エリック・ジョーンズCEO

Innovative Siliconのマーク・エリック・ジョーンズCEO