数字よりも中身がすごいんです──ATI Technologiesが「R520」こと新GPU「RADEON X1000」シリーズ発表:グラフィックスチップ(3/5 ページ)

» 2005年10月05日 22時14分 公開

[笠原一輝,ITmedia]

リングバスアーキテクチャの採用で仮想的な512ビットバスを実現

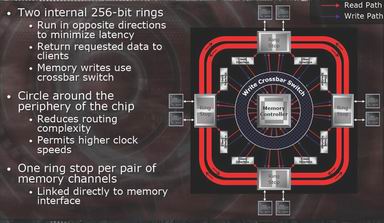

RADEON X1000シリーズのもう1つの大きな特徴は、新しいメモリバスアーキテクチャにある。ATIが“リングバス”と呼ぶこの方式では、メモリコントローラの周辺にメモリが円上に配置されており、それぞれのメモリをリングバスと呼ばれる専用の双方向の256ビットバスで接続する形状をとっている。

実際にメモリと接続されるのは、メモリコントローラそのものではなく「リングストップ」と呼ばれるリングバス上に接続されているアレイである、という点だ。実際の動作を見てみよう。GPUの演算器がメモリコントローラに対してアクセスする場合、まずメモリコントローラから目的のメモリが用意されているリングストップに対して要求が行われる。次にリングバスを経由して、GPUの演算器に近いリングストップへ転送が行われ、リングストップからGPUの演算器のデータが渡されるという流れになる。

このリングバスのメリットは、GPUとメモリ間のピン数を減らすほか、メモリの高速動作が可能になる。実際、RADEON X1000シリーズでは、最高1.5GHzでGDDR3を動作できることになっている。なお、メモリは32ビットバス8チャネルという構成になっている。これも従来の言いかたをするのであれば「メモリバス幅は256ビット」ということになる。

Copyright © ITmedia, Inc. All Rights Reserved.

SpecialPR

SpecialPR

アクセストップ10

2024年05月03日 更新

- サンワ、ペンを持つように操作できるペン型マウス (2024年05月01日)

- Intel N100搭載のChromebookは本当に重たくない? Lenovo IdeaPad Flex 3i Gen 8で動作をチェック! (2024年05月02日)

- Core i9搭載のミニPC「Minisforum NAB9」は最大4画面出力に対応 ワンタッチでカバーも取れる その実力をチェックした (2024年05月01日)

- パッと見で分からない細かいこだわりも バッファロー開発陣に聞くWi-Fi 7ルーター「WXR18000BE10P」の秘密【後編】 (2024年05月01日)

- スター・ウォーズの日間近! 「albos Light&Speaker」スター・ウォーズモデルが登場 (2024年05月02日)

- サンワ、体にフィットするコンパクトな回転座椅子 (2024年05月02日)

- 11年ぶりに出会った“本格的”Android搭載液タブ XPPen「Magic Drawing Pad」をプロイラストレーターがレビューして分かったアレコレ (2024年04月30日)

- かんたん設定のWi-Fi 6対応ルーター エントリーモデルがバッファローから登場 (2024年05月02日)

- トロンボーン奏者の中川英二郎氏が語る音楽/起源/進化、そしてテクノロジー (2024年05月02日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

最新トピックスPR

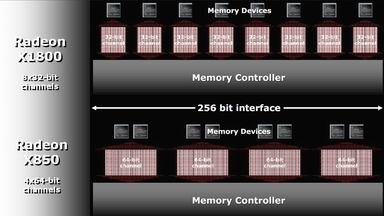

RADEON X1000シリーズのメモリインタフェースはX850と同じ256バス幅であるが、その構成は32ビット×8チャネルとなっている

RADEON X1000シリーズのメモリインタフェースはX850と同じ256バス幅であるが、その構成は32ビット×8チャネルとなっている