「電力効率性能に優れた新時代の幕開け」──IDF Japan 2006初日基調講演:IDF Japan 2006

Intelが開発者向けに開催する技術イベントであるインテル デペロッパー・フォーラム(IDF)は米国を皮切りに世界各国で順次行われる。

今回のIDF Japan 2006も、先月サンフランシスコで開催されたIDF Spring 2006の世界ツアーの一環であり、米国外で開かれるIDFのトップバッターになる。米国のIDF開催から日も浅いため、新しい情報は少ないものの、米国IDFで取り上げられた話題が「興味の冷めないうちに」日本語で聞ける、というメリットがある。

初日に行われた基調講演では本社でワールドワイドのセールス&マーケティング統括本部長の任にあるアナンド・チャンドラシーカ上席副社長が登壇した。チャンドラシーカ氏は日本がインターネット、そしてブロードバンドの先進国であり、IT革命の先頭を走る国の1つであると述べてから、現在直面している大きな技術課題である消費電力の問題を取り上げた。

これまでCPUはただひたすら絶対性能が求められていた。性能向上を図るために半導体の製造プロセスは微細化し、それに伴なう動作電圧低下の恩恵もあって、CPUの動作クロック引き上げに伴う消費電力の上昇は看過されてきた。

しかし、3GHzを超えたあたりから消費電力の問題がついに無視しえないものとなり、発想の転換が求められることになる。そうして出た結論が「CPUのマルチコア化」だ。

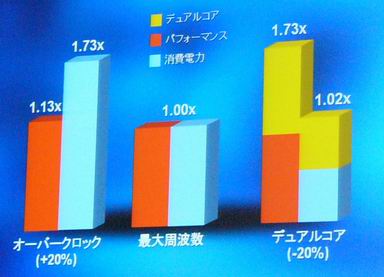

半導体の性能を引き上げるために、定格を超えて動作クロックを引き上げるオーバークロックは、それに伴う消費電力の増大とバランスよくトレードオフしない。Intelの試算では、20%のオーバークロックがもたらす性能上のゲインは13%に過ぎず、代わりに73%の消費電力増大をもたらす。しかし、逆に動作クロックを20%引き下げると13%の性能低下でとどまるにもかかわらず、消費電力はほぼ半減するという。

半減した消費電力の分でもう1つCPUコアを追加すれば、消費電力を据え置いたままで大幅な性能向上(73%アップ)が得られる。これがマルチコア化の基礎となる原理だ。

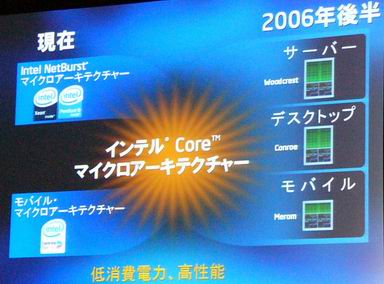

この原理に、Intelの最新の半導体プロセス技術、プラットフォーム技術を組み合わせて生まれたのが、Intel Coreマイクロアーキテクチャである。Intel Coreマイクロアーキテクチャは、処理効率の向上を念頭において開発されたもので、1命令あたりの消費電力を486プロセッサ相当まで戻すことに成功した。同マイクロアーキテクチャは、モバイルPC、デスクトップPC、サーバのそれぞれに最適化されたCPUとして、今年の第3四半期から供給が開始される予定だ。

IntelはCPUのデュアルコア化、そしてマルチコア化を促進するためにプラットフォーム戦略を推進する。モバイルPC向けのプラットフォームであるCentrino Duo、デジタルホーム向けのViivに続き、デジタルエンタープライズ(企業向けクライアント)のプラットフォームブランドを今年の半ばに立ち上げる。

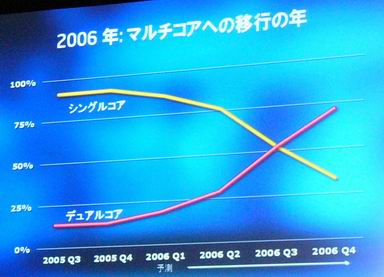

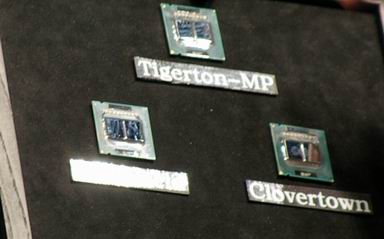

こうした施策により、今年の後半にはデュアルコアプロセッサの出荷割合がシングルコアを超えるとIntelは予想している。2007年前半はクアッドコア(4コア)CPUをリリースする予定であり、さらにマルチコア化、メニーコア化を推進していく。また、こうしたマルチコア路線を支える基盤技術の1つとして、ソフトウェアのマルチスレッド化をインテルは積極的に支援していく。

CPUのデュアルコア化やIntel Coreマイクロアーキテクチャの導入によりCPUの消費電力は下がる。しかし、これは逆に、プラットフォーム全体から見たときに、CPU以外の部分の消費電力を削減しなければ、全体の消費電力は下がらなくなることを意味する。

プラットフォームカンパニーであるIntelは、単にCPUの消費電力を引き下げるだけでなく、プラットフォーム全体の低消費電力化を推進し、電力効率性能に優れた新時代コンピューティング時代の幕開けを行いたいと述べ、チャンドラシーカ上席副社長はキーノートを締めくくった。

関連記事

- 低消費電力へシフトするIntelをアピールする「IDF Japan 2006」始まる

- 2006年はWoodcrestとAverillで勝負するインテル──4コアはやっぱり来年

- 次世代Centrino「Santa Rosa」の詳細が明らかに

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- 「IBMはテクノロジーカンパニーだ」 日本IBMが5つの「価値共創領域」にこだわるワケ (2024年04月23日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- Googleが「Google for Education GIGA スクールパッケージ」を発表 GIGAスクール用Chromebookの「新規採用」と「継続」を両にらみ (2024年04月23日)

- バッファロー開発陣に聞く「Wi-Fi 7」にいち早く対応したメリット 決め手は異なる周波数を束ねる「MLO」【前編】 (2024年04月22日)

- ロジクール、“プロ仕様”をうたった60%レイアウト採用ワイヤレスゲーミングキーボード (2024年04月24日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- ゼロからの画像生成も可能に――アドビが生成AI機能を強化した「Photoshop」のβ版を公開 (2024年04月23日)

- MetaがMR/VRヘッドセット界の“Android”を目指す 「Quest」シリーズのOSを他社に開放、ASUSやLenovoが独自の新ハードを開発中 (2024年04月23日)

Intel CoreマイクロアーキテクチャのデュアルコアCPU「Woodcrest」を搭載したサーバを紹介するチャンドラシーカ上席副社長

Intel CoreマイクロアーキテクチャのデュアルコアCPU「Woodcrest」を搭載したサーバを紹介するチャンドラシーカ上席副社長 オーバークロックすると性能が向上する以上に消費電力が増す。クロックを下げると性能が下がる以上に省電力化が進む。省電力が進んだ分コアを増やすと消費電力を増やすことなく性能向上を実現できる

オーバークロックすると性能が向上する以上に消費電力が増す。クロックを下げると性能が下がる以上に省電力化が進む。省電力が進んだ分コアを増やすと消費電力を増やすことなく性能向上を実現できる Intel Coreアーキテクチャはモバイル向けCPUのMerom、コンシューマーデスクトップ向けのConroe、ワークステーション向けのWoodcastとなって2006年後半に投入される予定だ

Intel Coreアーキテクチャはモバイル向けCPUのMerom、コンシューマーデスクトップ向けのConroe、ワークステーション向けのWoodcastとなって2006年後半に投入される予定だ インテルはビジネスクライアント向けプラットフォームブランド(開発コード名:Averill)を2006年後半に投入する予定だ

インテルはビジネスクライアント向けプラットフォームブランド(開発コード名:Averill)を2006年後半に投入する予定だ インテルの計画では2006年第3四半期にシングルコアとデュアルコアの割合は拮抗し、2006年待つまでにデュアルコアのシェアは70%に達することになっている

インテルの計画では2006年第3四半期にシングルコアとデュアルコアの割合は拮抗し、2006年待つまでにデュアルコアのシェアは70%に達することになっている 2007年前半に投入されるクアッドコアCPU。デスクトップPC向けのKentsfield、DPサーバ向けのClovertown、MPサーバ向けのTigertonが並ぶ

2007年前半に投入されるクアッドコアCPU。デスクトップPC向けのKentsfield、DPサーバ向けのClovertown、MPサーバ向けのTigertonが並ぶ