「Torrenza」「Fusion」にかける新生AMD

年の瀬の12月20日、日本AMDは米国本社からワールドワイドセールス/マーケティング最高責任者のヘンリー・リチャード氏を招き、先週14日に米国で開催され得たアナリストデイの内容を日本の関係者に対して説明。あわせて、11月15日に日本法人社長に就任した森下正敏新社長(旧ATIテクノロジーズジャパン社長)が紹介された。

ほぼ1人でプレゼンテーションを行ったリチャード氏は、2006年にAMDが達成したこととして、念願だった企業向け市場への本格的な参入を果たしたことを挙げた。その鍵となったのは、グローバル規模で展開するPCベンダにたいするOEMの増加で、それを象徴するのがデルの採用であることは間違いない。従来、AMDが得意としていた市場は先進国のチャネル市場だったが、グローバルOEMの増加で、途上国市場も含めた全市場セグメントでバランスのとれた売り上げ構成比に近づきつつあるようだ。

2006年におけるもう1つの大きな出来事は、グラフィックスチップベンダであるATI Technologiesを買収したことだ。ATI Technologiesは、PC向けGPU「RADEON」シリーズやチップセットで知られるほか、XboxやWiiといったゲーム機向けのグラフィックスチップ、ソニーやサムスン製の薄型TVへXilleonシリーズのSOCを提供している。従来、コンピュータ市場に強かったAMDが、豊富なコンシューマー製品を持つATI Technologiesを買収することで、コンシューマー市場からコンピュータ市場まで横断的なプロセッサの品ぞろえを持つ「プロセッシングパワーハウス」へと変貌したのが2006年であるとしている。

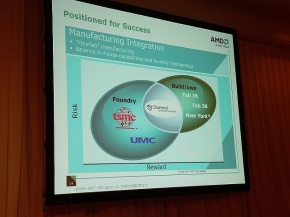

もちろん2007年は、Windows Vistaをきっかけにさらなる飛躍を目指すが、それでも最大のプライオリティはサーバー市場とOpteronプロセッサに置かれる見込みだ。この飛躍を実現するためには、製造能力の強化が不可欠だが、2007年も2006年と同じく3つの製造形態を維持するという。ドイツのドレスデンにある自社Fab(自社工場)、シンガポールのチャータード・セミコンダクターへの製造委託(AMDの自社技術をベースにした生産委託)、そしてTSMCやUMCといった外部ファウンダリの活用である。

ドレスデンに隣接する2つの工場のうち、300ミリウエハを用いる新しいFab 36は、現在90ナノメートルプロセスルール(ナノプロセス)から65ナノプロセスへの転換を行っている。すでに65ナノプロセスによる最初のシリコンが出荷されており、間もなく市場に登場するものと思われる。Fab 36が完全に65ナノプロセスへ切り替わるのは2007年半ばを見込む。一方、これまで200ミリウエハで90ナノプロセスのプロセッサを量産してきたFab 30は、現在300ミリウェファを用いた工場へと転換中だ。2007年前半には300ミリウエハを用いたFab 38へと生まれ変わる予定になっている。この2カ所に加え、現在米国ニューヨーク州への工場建設を検討している。

これら自社Fabとシンガポールのチャータード・セミコンダクターでは主にOpteronやAthlon 64、Turion 64といったx86系CPUが量産される。外部のファウンダリで作られるのは、主に旧ATI Technologiesの製品だ。ATI Technologies製品がこれらのファウンダリで製造されてきたという歴史的な経緯に加え、AMDの自社FabはCPUのような高性能・高価格の半導体製造にフォーカスしており、必ずしもチップセットやGPUの量産には適していない(コストが高い)ということも理由だと思われる。したがって単純な工場のキャパシティという理由だけではなく、当面ファウンダリへの生産委託は継続されるだろう。

AMDのFab36は65ナノプロセルルールへの移行を進めており、2007年半ばにはフル生産が可能になる予定。Fab30は300ミリウエハ生産に対応するFab38の稼動を2007年第1四半期にスタートさせる予定だ

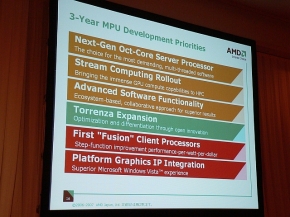

AMDのFab36は65ナノプロセルルールへの移行を進めており、2007年半ばにはフル生産が可能になる予定。Fab30は300ミリウエハ生産に対応するFab38の稼動を2007年第1四半期にスタートさせる予定だこうした量産体制で製造される、今後3年間の製品開発上の優先項目として、

(1)次世代のサーバー向け8コアCPU

(2)GPUが持つ高い浮動小数点演算性能をHPC分野に応用するStream Computing

(3)パートナーとの協業によるソフトウェア最適化の推進

(4)Torrenza構想の拡張

(5)第1世代のクライアント向けFusionプロセッサ

(6)Windows Vista体験を向上させるグラフィックスIPのプラットフォームへの統合

の6点を挙げた。

AMDは2007年半ばに、65ナノプロセスを用いたクワドコアCPUをリリースすることを明らかにしている。Socket F対応の2ウェイおよび8ウェイサーバー用CPU(開発コード名Barcelona)と、Socket AM2対応のユニプロセッササーバ用CPU(同Budapest)が2007年半ばに、そして2008年には2ウェイと8ウェイ用のクワドコアCPUがリフレッシュされる(同Shangai)見込みだ。8コアCPUは、さらにこの後、2009年以降になる。

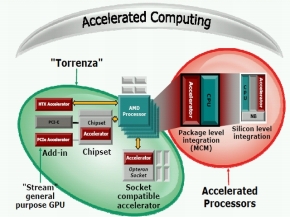

Torrenzaは、プラットフォーム上、目的に応じて性能的、あるいはコスト的に最適な場所に、特定の処理を高速化するアクセラレータを配置しようというアイデアである。アクセラレータを配置する場所としては、CPUと同一のダイ上、CPUと同じパッケージ内の別ダイ(MCP)、CPUソケットを複数用意しそこにCPUとピン互換のアクセラレータを乗せる、Hyper-Transport対応のソケット規格であるHTXのカードとして、汎用のPCI Expressバス上など、様々な形が考えられる。たとえば2のStream Computingは、PCI Express接続のGPUをそのまま浮動小数点演算のコプロセッサとして利用しよう、というアイデアである。

クライアント向けのプロセッサ構想であるFusionは、AMDのCPUコアとATIのGPUに関するIPを1つのプロセッサという形にまとめようというもの。これにより省電力と、高コストパフォーマンスを狙う。とくにノートPCに最適なソリューションだと考えられている。

AMDの将来プランには、特定処理の高速化を図るアクセラレータや、グラフィックスコアなど、いわゆる汎用のCPUコア以外のチップをCPUと統合するアイデアが目立つ。おそらく現在のCPUコアを8つ、あるいはそれ以上集積しても、サーバーやHPCのようにひたすら計算能力が求められる市場以外では、受け入れられないと考えているのだろう。2010年あたりまでは、コアの数が増えていくものの、それ以降はコアの数がいくつかが重要なのではなく、どんなアクセラレータを組み合わせるかが重要になるという。このようなヘテロジニアスなメニーコアプロセッサがAMDの描く未来像のようだ。

関連記事

Torrenza対応「コプロセッサ搭載HTXカード」が姿を見せた!──AMDの次世代CPU戦略

Torrenza対応「コプロセッサ搭載HTXカード」が姿を見せた!──AMDの次世代CPU戦略

AMDの米国本社で行われたテクニカルイベントではクワッドコアを見据えた「4x4」などAMDのユニークがアイデアが明らかに。「AMDがATIを買収か?」についても言及した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- もう全部、裏配線でいいんじゃない? 「ASUS BTF DESIGN」が示す自作PCの新しい形 (2024年04月19日)

- ノートPCに外付けキーボードを“載せて”使える「タイプスティックス/打ち箸」に新色 (2024年04月18日)

- バッファロー製Wi-Fiルーターに脆弱性 対象機種は今すぐファームウェア更新を (2024年04月17日)

- さらなる高速化を実現! PCI Express 5.0接続SSDの新モデル「Crucial T705」を試して分かったこと (2024年04月18日)

- ついに8K対応した「Insta360 X4」の画質をX3と1インチ360度版で比較 今買うべき全天球カメラだと確信した (2024年04月16日)

- SwitchBotのミニプラグに不具合 「断続的にオン/オフを繰り返す、異音」などで該当製品の交換を呼びかけ (2024年04月17日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- Core Ultra搭載の「Let's note FV5」を徹底検証 プレミアムモバイルの実力は? (2024年04月19日)

- 話題になったトラックボール「IST」も登場! エレコムのPC周辺機器が最大21%お得に買える (2024年04月19日)

- アイロボットが4万円切りの「水拭き対応ロボット掃除機」を投入 “一家に1台”を目指す (2024年04月17日)