Intelが45ナノ「Penryn」ダイ画像を公開:元麻布春男のWatchTower

米国時間の1月26日、Intelは45ナノメートルプロセスルール(45ナノプロセス)を採用した5種類のマイクロプロセッサを試作し動作を確認したと発表、あわせてそのダイ写真を公開した。かねてよりIntelは、2007年後半から45ナノプロセスによる量産を開始すると表明しており、その計画に変更がないことを明らかにした。45ナノプロセスによる試作例としては、2006年1月にSRAMチップのサンプルを公開しているが、今回の試作品はマイクロプロセッサであり、着実に実用化が近づいていることがうかがえる。

半導体の微細化は、ゲート絶縁膜を極限まで薄くすることで実現されるが、最新の65ナノプロセスでは原子数個分のレベルにまで到達している。ここまできてしまうとこれ以上薄くすることは難しい。製造プロセスをこれ以上を微細化することが困難であることと同義であるとともにムーアの法則を継続できないということも意味する。また、薄くなった絶縁膜は、電流の透過によるリーク電流の問題も招く。

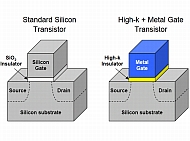

こうした問題を克服する1つのアイデアは、厚くしても従来の二酸化シリコン製絶縁膜と同等の電界効果を得られるHigh-k(高誘電率)材料を絶縁膜に用いることだ。しかし、多くのHigh-k材料は1960年代から使われてきた電極材料である多結晶シリコンによるゲート電極と相性が悪いという問題があった。Intelは、High-kゲート絶縁膜と組み合わせられるメタルゲート電極を開発したと2003年に発表し、これを45ナノプロセスから採用すると表明していた。

今回発表された45ナノプロセスによるマイクロプロセッサは、まさにこのHigh-k絶縁膜とメタルゲート電極を組み合わせたもので、絶縁膜にはハフニウム系の材料を用いる。電極材料については、複数の金属を組み合わせた複合金属材料をNMOS、PMOSそれぞれに最適化して用いるとしているが、詳細は明らかにしていない。露光に従来と同じ波長193ナノのドライリソグラフィー装置を用いるため、シリコンスループット(生産性)も維持される見込みだ(ただし、将来的には液浸露光装置を採用する可能性を否定していない)。

この新しい45ナノプロセス(P1266と呼ばれる)により、現在の65nmプロセスに対して、トランジスタ密度が約2倍、トランジスタのスイッチング速度が約20%向上する。と同時に、ソースとドレイン間のリーク電流が約5分の1に、ゲート絶縁膜でのリーク電流が約10分の1にそれぞれ削減される。また、微細化と合わせ、スイッチング電力はおおよそ30%削減されるとしている。製造に従来と同じバルクウェファが使える(高価なSOIウェファが要らない)ことと、トランジスタ密度が2倍になること(これはダイ面積の縮小を可能にする)から考えて、P1266は性能や消費電力だけでなく、価格競争力の点でも優れたポテンシャルを持たせるものと思われる。

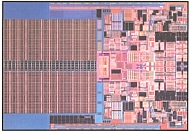

P1266で製造されるCPUは、従来から“Penryn”という開発コード名が伝えられてきた。Penrynは、サーバー/ワークステーション、デスクトップPC、モバイルPCのそれぞれの分野向けに提供されるCPUのファミリー名。冒頭で述べた5種は、モバイルPC向けのデュアルコア、デスクトップPC向けのデュアルコアとクアッドコア、2Pサーバー/ワークステーション向けのデュアルコアとクアッドコアを指す。Penrynは、現行CPUのシュリンク(新しいマイクロアーキテクチャを採用しているわけではない)とされていることから考えて、ダイそのものはデュアルコアで、クアッドコアプロセッサはこのダイを2個内蔵するものと思われる。

この次世代Core 2プロセッサファミリーについても、いくつかの情報が公開された。まずトランジスタ数はデュアルコアで4億1000万個、クワドコアで8億2000万個とされる。キャッシュ容量は最大12Mバイトとされているが、この数字はおそらく2個のダイを合わせたものだろう(ダイあたり6Mバイト、1コアで3Mバイト)。また、2006年秋のIDFで明らかにされたとおり、約50個のSSE4命令が搭載される。もちろん、コアの動作クロックも上がる見込みだ。

この45ナノプロセスによる量産は、2007年後半にオレゴン州のD1Dと、アリゾナ州のFab 32でスタートし、2008年前半にイスラエルのFab 28が加わる予定だ(Fab 32とFab 28は新しい工場として現在建設中)。Intelでは、High-kゲート絶縁膜とメタルゲート電極の技術で先行していることに自信を持っており、他社が追いつくのは1世代先の32ナノプロセス、あるいはそれ以降になると予想している。

関連記事

クアッドコアは11月に登場、80コア搭載CPUのプロトタイプも公開──オッテリーニ氏基調講演

クアッドコアは11月に登場、80コア搭載CPUのプロトタイプも公開──オッテリーニ氏基調講演

「Intel Developer Forum Fall 2006」がサンフランシスコで9月26日(現地時間)にスタート。Intel 社長兼CEOのポール・オッテリーニ氏のキーノートスピーチでは、クアッドコア(4コア)CPUが紹介された。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ノートPCに外付けキーボードを“載せて”使える「タイプスティックス/打ち箸」に新色 (2024年04月18日)

- バッファロー製Wi-Fiルーターに脆弱性 対象機種は今すぐファームウェア更新を (2024年04月17日)

- もう全部、裏配線でいいんじゃない? 「ASUS BTF DESIGN」が示す自作PCの新しい形 (2024年04月19日)

- さらなる高速化を実現! PCI Express 5.0接続SSDの新モデル「Crucial T705」を試して分かったこと (2024年04月18日)

- ついに8K対応した「Insta360 X4」の画質をX3と1インチ360度版で比較 今買うべき全天球カメラだと確信した (2024年04月16日)

- SwitchBotのミニプラグに不具合 「断続的にオン/オフを繰り返す、異音」などで該当製品の交換を呼びかけ (2024年04月17日)

- アイロボットが4万円切りの「水拭き対応ロボット掃除機」を投入 “一家に1台”を目指す (2024年04月17日)

- 「JBL GO 4」でBluetoothスピーカーデビュー! 累計出荷台数5700万台を突破した人気製品の最新モデルを試す (2024年04月17日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- 無線LANルーター「Aterm」シリーズの一部に複数の脆弱性 設定変更や買い替えをアナウンス (2024年04月11日)