徐々に見えてくるNehalem──8Mバイトの3次キャッシュは「みんなで使う」:元麻布春男のWatchTower (1/2 ページ)

30Mバイトのキャッシュを実装する「Tukwila」、6コアを搭載する「Dunnington」

上海で行われるIDFを4月に控え、Intelは「Intel Architecture Press Briefing」を開催した。従来は世界各地を巡回していたIDFだが、全世界的な「経費節約」もあって、現在のところ春に中国、秋に米国と台湾という年3回の開催になっている。中国で行うIDF開催にはIntel本社のお膝元でもある米国プレスが参加しにくいことを配慮して、事前にそのエッセンスを伝えるために、この「Press Briefing」が開かれると聞いている。北京で開催された2007年にも同様なセッションが行われている。

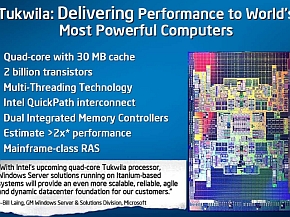

今回のブリーフィングを取り仕切ったのが同社デジタル・エンタープライズ事業部だったためか、最初に紹介されたのは「Tukwila」関連の話題だった。最新版のItaniumとなるTukwilaは、トータルで30Mバイトのキャッシュを持つクアッドコアCPUとなる予定だ。20億個のトランジスタを集積し、IA-64としては初めてマルチスレッディング技術(Pentium 4に採用されたハイパー・スレッディング技術のように、1コアを2つの論理プロセッサに見せかける技術)を採用し、さらに、2つのメモリコントローラをCPUに内蔵することで十分なメモリ帯域も確保するといわれている。外部インタフェースとしては「QuickPath Interconnect」(QPI)を導入する予定で、QPIを採用して登場する予定の次世代Xeon MPなどとプラットフォームを統一しやすくなる。

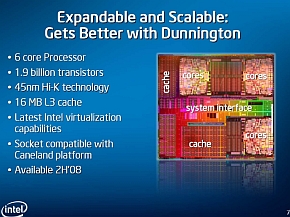

そのXeon MPだが、2008年後半にリリースされる「Dunnington」(開発コード名)は、新世代のQPIではなく、既存の“Caneland”プラットフォームとピン互換性を持つとされている。その一方で、IntelのCPUとしては初めて6コアを組み込むほか、6コアで共有される16Mバイトの3次キャッシュを備えるなど、Tigertonに比べてアーキテクチャは大幅に進化する。

ただ、コアそのものは基本的にPenryn相当なので、2次キャッシュは2コアでの共有となる(2×3=6コア)。2次キャッシュの容量などは公開されていないが、Dunningtonのダイ写真を見る限り3Mバイト程度と推察できる。1つのダイに6コアと大容量の3次キャッシュを持つDunningtonも、Tukwilaに匹敵する19億トランジスタを集積した巨大なチップになる。海外の参加者からDunningtonをハイエンドデスクトップPC向けにリリースする可能性を問われたが、少なくとも今の時点においてIntelは否定している。

SMTと並列処理の強化で33%のパワーアップを図るNehalem

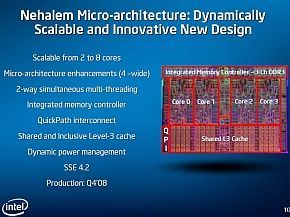

このDunningtonまでがコアマイクロアーキテクチャを踏襲することになるが、2008年の終わりまでに登場する予定のNehalemから新しいマイクロアーキテクチャが採用される。ただし、こちらもコアの基本的な構造はPenryn世代ベースにして強化される。

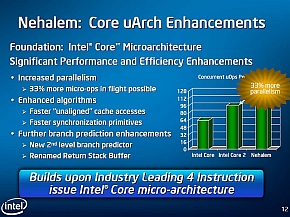

その強化ポイントとしてIntelは、

- 並列処理の強化により、コアで処理中のマイクロ命令(μOps)の数が33%増加する

- アルゴリズムの改善によるキャッシュに対する不整列アクセスと同期処理の高速化

- 分岐予測のさらなる強化

- SSE4.2命令の搭載

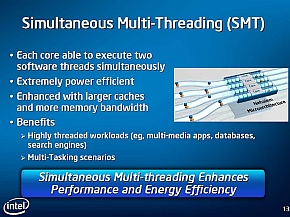

- SMT技術(マルチスレッディング技術)の採用

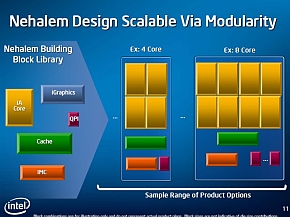

などを挙げる。IntelはNehalemのコア数を2〜8個としているが、SMTを併用することでソフトウェアからは4〜16個のコアを持つように見えることになる。

まったくの新開発であるはずのNehalemがPenrynをベースとする理由としてIntelは、SMTを採用するだけでも大きな変更であることに加え、外部構造が大きく変化することを挙げている。Nehalemは、メモリコントローラを内蔵すると同時に、外部インタフェースに従来のFSBアーキテクチャをやめて、Tukwilaで紹介したQPIを採用する予定だ。

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- もう全部、裏配線でいいんじゃない? 「ASUS BTF DESIGN」が示す自作PCの新しい形 (2024年04月19日)

- ノートPCに外付けキーボードを“載せて”使える「タイプスティックス/打ち箸」に新色 (2024年04月18日)

- バッファロー製Wi-Fiルーターに脆弱性 対象機種は今すぐファームウェア更新を (2024年04月17日)

- さらなる高速化を実現! PCI Express 5.0接続SSDの新モデル「Crucial T705」を試して分かったこと (2024年04月18日)

- ついに8K対応した「Insta360 X4」の画質をX3と1インチ360度版で比較 今買うべき全天球カメラだと確信した (2024年04月16日)

- SwitchBotのミニプラグに不具合 「断続的にオン/オフを繰り返す、異音」などで該当製品の交換を呼びかけ (2024年04月17日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- 話題になったトラックボール「IST」も登場! エレコムのPC周辺機器が最大21%お得に買える (2024年04月19日)

- アイロボットが4万円切りの「水拭き対応ロボット掃除機」を投入 “一家に1台”を目指す (2024年04月17日)

- Core Ultra搭載の「Let's note FV5」を徹底検証 プレミアムモバイルの実力は? (2024年04月19日)