「Larrabee」の姿が見えてきた:元麻布春男のWatchTower

“論文”で概要が明らかになったLarrabee

Larrabeeは、インテル初のメニーコアプロセッサとして開発が進められてきた。まずはグラフィックスカードに使われるスタンドアロンのGPUとして、2009〜2010年に製品化される見込みだ。今回、米国計算機学会(ACM)のサイトに掲載された論文で紹介されている情報は、そのアーキテクチャの概要に関するものであり、製品に関する発表ではない。

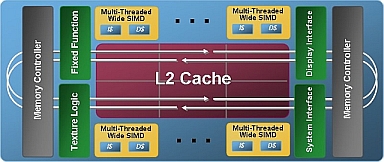

インテルが明らかにしたLarrabeeのブロックダイアグラム。黄色のエリアで示されているのが「Multi-Threaded Wide SIMD」、緑色で示された「System Interface」、「Display Interface」、「Texture Logic」、「Fixed Function」がLarrabeeに実装される固定機能の部分となる

インテルが明らかにしたLarrabeeのブロックダイアグラム。黄色のエリアで示されているのが「Multi-Threaded Wide SIMD」、緑色で示された「System Interface」、「Display Interface」、「Texture Logic」、「Fixed Function」がLarrabeeに実装される固定機能の部分となるメニーコアアーキテクチャを採るLarrabeeのブロックダイアグラムには、プログラマブルなx86コア(ブロックダイアグラムで黄色に示された“Multi-Threaded Wide SIMD”と書かれた部分)、メモリコントローラ、固定機能部(同じく、緑色で示された部分)と、これらを結ぶリングバスで構成される。x86コアは2次キャッシュメモリを通じてリングバスに接続されており、リングバスを通じてほかのコアに属する2次キャッシュメモリを参照できる(物理的には、1つの2次キャッシュメモリをコアごとに分割して利用する)。

2次キャッシュメモリをコア間のデータパスとして利用するという点では、コアマイクロアーキテクチャに通じる部分があるが、今回の発表によるとLarrabeeの2次キャッシュメモリは、各コアあたり256Kバイトで固定的に分割される。したがって、8コアであれば2次キャッシュメモリは2Mバイト、16コアであれば4Mバイトということになるが、最終的に登場する製品の具体的なコア数と2次キャッシュメモリの容量は明らかにされていない。

リングバスは、双方向合わせて1024ビット幅とインテルの資料では述べられている。上りと下り、それぞれの方向あたりでは512ビット幅となる。ただし、16コアを超える場合は、コア部だけを結ぶリング(short linked)を追加するようだ。このリングバスに接続されるx86コアは、スカラー部とベクター部(VPU)に分けられる。スカラー部とベクター部は、それぞれが利用するスカラーレジスタとベクターレジスタに独立している。しかし、1次キャッシュメモリ(命令キャッシュ32Kバイト+データキャッシュ32Kバイト)は共有しているので、1次キャッシュメモリを通じてスカラー部とベクター部でデータをやり取りできる。

“P5世代”Pentium+αとなるアーキテクチャ

Larrabeeが「x86互換のメニーコア」と呼ばれるのは、このスカラー部がx86互換であるからだ。インテルはLarrabeeのスカラー部について、Pentium(P5)で使われていたパイプラインの改良型と述べている。スカラー部はPentium互換(MMX命令が追加される前の世代)の命令セットをベースに、64ビット拡張やキャッシュ制御命令などの拡張を加え、マルチスレッド技術を追加しているようだ。Larrabeeについてよくいわれることの1つは、「x86互換の必要があるのか」ということだが、意外とPentiumのアーキテクチャを流用したから、ということがその答えなのかもしれない。

パイプラインの段数についても、Pentiumと同様のショートパイプラインだとインテルは説明している。Pentiumのパイプラインは、整数演算が5段、浮動小数点演算でも8段と、P6マイクロアーキテクチャ以降に比べると格段に短い。一方、Pentiumは、uパイプとvパイプの2つの実行パイプラインを持ち、同時に2命令を実行できるが、ほぼすべての命令が実行可能なuパイプに対し、vパイプはシンプル命令しか実行できないという制限があった。

Larrabeeのコアにこの制限がそのまま当てはまるのかは不明だが、すべての命令をサポートするprimaryパイプラインと、サブセットのサポートとなるsecondaryパイプラインで構成されることが明らかになっている。インテルは、こうした非対称構成のパイプラインについて、コンパイル時における命令のペアリング(2つのパイプラインそれぞれに対する命令の割り当て)は、実行時にペアリングを行う「out of orderコア」より効率的だとしている。仮にペアリングができなかったとしても、機能が限られる分だけsecondaryパイプラインはシンプルで、トランジスタ数も少ないため、1命令実行となった(secondaryパイプラインがアイドル)場合の損失は比較的小さいという。

Larrabeeのスカラー部は、マルチスレッド技術の併用により、最大で4スレッドの同時実行をサポートする。使用するレジスタも4スレッドで独立しており、ストール時のペナルティを低減することが可能だ。

スカラー部がMMXやSSEをサポートしない代わりに、Larrabeeのコアは専用のベクター演算ユニット(VPU)を持つ。VPUの命令セットについても具体的には明らかにされていないが、16-wideのVPU(16個の32ビットデータ要素を同時に扱える)だといわれている。8ビットや16ビットのデータを扱う場合は、キャッシュメモリから読み込むときに、32ビットの整数、あるいは浮動小数に変換されるため、別途変換する必要がない。また、キャッシュメモリ上のデータサイズを小さく抑えられるため、キャッシュメモリの利用効率が向上する。同時に扱う16個の32ビットデータ要素は、連続したアドレスからロードするだけでなく、個別のアドレスからロードすることも可能だ。ベクター演算の実行では、マスクレジスタを併用することで、レジスタやメモリの一部のみの結果を書き込むこともできる。

このプログラマブルなコアを最大限活用し、固定機能を最小限で済ませようというのが、Larrabeeの基本的なアーキテクチャだ。Larrabeeが持つ固定機能のうち、バスインタフェース(PCI Express)やディスプレイインタフェースは必須とされている。グラフィックス機能のうち固定機能として処理されるのは、テクスチャのフィルタリングなどごく一部だ。多くのGPUでは固定機能として処理されるセットアップやラスタライザも、Larrabeeではプログラマブルコアを利用したソフトウェアで処理される。

Larrabeeは“GPGPU”の鏡像なのか

Larrabeeのソフトウェアレンダラで最も特徴的なことは、「Binning」と呼ばれるアーキテクチャを採ることだ。Binningとは、描画領域を小さな領域に分けて処理することで、「タイリング」あるいは「チャンキング」などとも呼ばれる。描画領域を小分けにすることで、それぞれのコアで処理するデータが2次キャッシュメモリに収まるため、処理速度の低下が抑えられるというメリットがある(レンダラーからは、見かけのメモリ帯域が2次キャッシュメモリの容量と同等になる)。

1990年代の半ばに、PC用の3Dグラフィックスアクセラレータが登場するまで、PC上での3Dグラフィックスは、すべてソフトウェアで処理されていた。登場当初の3Dグラフィックスアクセラレータは、ソフトウェアで行っていた3Dグラフィックス処理のうち、特定の機能をハードウェアで置き換えることで、処理そのものの高速化を図ると同時に、CPUから3Dグラフィックス処理の重荷を取り除くものだった。

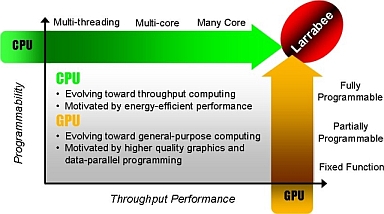

プログラマブルシェーダの概念を盛り込んだDirectX 8に対応したGPUがリリースされた2001年以降、3Dグラフィックスアクセラレータは年ごとにプログラマビリティを向上させ、いつしか名称も単にGPU(Graphics Processing Unit)と呼ばれるようになった。そして、さらに高度なプログラマビリティを目指して、汎用のCPUに近づこうとしている。

一方のCPUは、シングルスレッド性能の追求が、マイクロアーキテクチャとエネルギー効率の両面から限界に達し、マルチスレッド性能の追求に比重が移っている。並列性を追求したGPUに徐々に近づこうとしているわけだ。

Larrabeeは、高いプログラマビリティを備えるCPUと高い並列性を備えるGPUのそれぞれが持つ長所を取り込むことを狙って開発されている。ソフトウェアレンダリングの一部をハードウェアで置き換えるのではなく、自由度の高いソフトウェアレンダリングを高速化するためのプロセッサとして進化しようとしている、という見方もできるだろう。

高度なプログラマブルプロセッサとなるLarrabeeは、グラフィックス処理以外に、いわゆるGPGPU的な用途に利用することも可能だ。インテルはLarrabeeネイティブなコンパイラを提供し、アプリケーションプログラムから直接Larrabeeを利用できるようにもする。おそらく各種のライブラリも整備されるものと思われる。

今回公開された資料では、製品としてリリースされるLarrabeeの仕様は明らかにされておらず、その性能も不明だ。インテルはコア数の違いや、コアクロックの異なる複数のバージョンをリリースすることを示唆しており、性能にも一定の幅があると考えられる。参考値として挙げられているのは、1GHzで動作するLarrabeeが発揮する性能の目安として、解像度を1600×1200ドットに設定した「Half-Life 2」で60fpsを実現するのに必要なコア数は10個、同様に「F.E.A.R.」や「Gears of War」であれば25個、という数字だ。おそらく、このレベルが製品版で目標としている性能なのではないかと思われる。

関連記事

Intel、メニーコアプロセッサ「Larrabee」の概要を公開

Intel、メニーコアプロセッサ「Larrabee」の概要を公開

Intelがグラフィックス用途向けメニーコアプロセッサLarrabeeの概要を初めて公開した トップからボトムまでインテルがやります

トップからボトムまでインテルがやります

Intelのゲルシンガー氏が日本を訪れた。COMPUTEX TAIPEI 2008が来週から始まるという、このタイミングで、彼は日本人になにを伝えたかったのだろうか。 インテルの次世代プラットフォームを考える

インテルの次世代プラットフォームを考える

Intel 4シリーズチップセットやCentrino2と、徐々にではあるがインテルの次世代プラットフォームが姿を現しつつある。その概要をまとめた。 WiMAXとMoorestownで広がるモバイルデバイスの行動圏

WiMAXとMoorestownで広がるモバイルデバイスの行動圏

IDF 2007の2日めは「モバイル・デイ」がテーマだった。ここでは、ノートPC、UMPC、新しいカテゴリの小型デバイス、そしてWiMAXに関するIntelの発言をまとめていく。 「Nehalem」が動いたっ!──IDF初日基調講演から

「Nehalem」が動いたっ!──IDF初日基調講演から

年2回の開催から年1回となったIDF(北京は特別版ということで)。そのおかげで内容も充実している。リポート第2弾は「Penryn」「Nehalem」をカバーしよう。 ムーアの法則が終わる日──ゴードン・ムーア氏特別講演から

ムーアの法則が終わる日──ゴードン・ムーア氏特別講演から

Intel Developer Forum 2007が9月18日(米国時間)から始まった。初日はIntel CEOの基調講演などが行われたが、IDF 2007の第一報は「インテルといえばこの人」が登場した特別講演からお届けしよう。 インテルが“ナマPenryn”を日本で披露

インテルが“ナマPenryn”を日本で披露

「最も知られた人物の1人」とインテルが紹介するゲルシンガー氏が来日。話題盛りだくさんのIDF北京を総括した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- わずか237gとスマホ並みに軽いモバイルディスプレイ! ユニークの10.5型「UQ-PM10FHDNT-GL」を試す (2024年04月25日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- 「Surface Go」が“タフブック”みたいになる耐衝撃ケース サンワサプライから登場 (2024年04月24日)

- QualcommがPC向けSoC「Snapdragon X Plus」を発表 CPUコアを削減しつつも圧倒的なAI処理性能は維持 搭載PCは2024年中盤に登場予定 (2024年04月25日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- アドバンテック、第14世代Coreプロセッサを採用した産業向けシングルボードPC (2024年04月24日)

- AI PC時代の製品選び 展示会「第33回 Japan IT Week 春」で目にしたもの AI活用やDX化を推進したい企業は要注目! (2024年04月25日)

- ロジクール、“プロ仕様”をうたった60%レイアウト採用ワイヤレスゲーミングキーボード (2024年04月24日)