20メガワットエクサスケールは破壊的イノベーションで実現する:スマートフォンもスパコンになる!(20年前の)(1/3 ページ)

NVIDIAの破壊的イノベーションが20メガワットエクサを可能にする

NVIDIA CEOのジェン・スン・ファン氏は、米ワシントン州シアトル市で開催したハイパフォーマンスコンピューティング(以下、HPC)関連の技術会議「SC11」の基調講演に登場した。そこで、ファン氏は、エクサスケールスーパーコンピュータの実現に「破壊的イノベーション」が必要とした上で、今後のスーパーコンピュータ開発においては、「ノートPCなどと同じく、消費電力に関する許容範囲があってしかるべきだ」と述べた。ファン氏は、「20メガワット以下で設計」していく新しい価値基準の導入が必要と主張する。

SC11のキーノートに登場したNVIDIA CEOのジェン・スン・ファン氏(写真=左)。ファン氏は、イノベーションのジレンマを題材に、HPC市場が直面する新しい価値観を持った破壊的イノベーションの必要性を説いた(写真=右)

SC11のキーノートに登場したNVIDIA CEOのジェン・スン・ファン氏(写真=左)。ファン氏は、イノベーションのジレンマを題材に、HPC市場が直面する新しい価値観を持った破壊的イノベーションの必要性を説いた(写真=右)NVIDIAは、米国防総省の先端技術開発研究を担うDARPA(Defense Advanced Research Project Agency)主導のもと、2018年にエクサスケールスーパーコンピュータを実現する「Ubiquitous High Performance Computing」(UHPC)プログラムに参加する企業のうちの一社であり、自社で開発するARMコアとGPUコアを統合した“Echelon”(エシュロン)プロセッサの開発を進めていることは、2010年の「SC10」で明らかにしている。

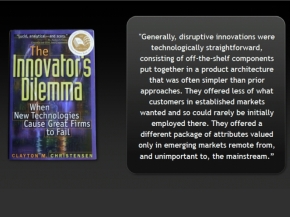

このUHPCプログラムでは、データセンターの消費電力を20メガワット以下と義務づけられており、同プログラムを実現するためには従来の価値基準を見直す必要があるとして、ファン氏はスーパーコンピュータ市場においても、ハーバード大学経営大学院教授のクレイトン・M・クリステンセン(Clayton M. Christensen)氏の著書「The Innovator's Dilemma: When New Technologies Cause Great Firms to Fail」(邦題「イノベーションのジレンマ − 技術革新が巨大企業を滅ぼすとき」)で説かれた「破壊的イノベーション」が必要とされているという。

クリステンセン氏の「イノベーションのジレンマ」は、1997年に刊行されたマーケティング論に関する著作で、優良企業が顧客の要望に応えて製品の改良を進めていく「持続的イノベーション」よりも、商品そのものの特色には劣るが従来製品の価値を破壊する新しい価値観を持った新興企業に主導権を奪われることがあるとしたもの。ファン CEOは、NVIDIAのこれまでを振り返り、同社がこの「破壊的イノベーション」でグラフィックス市場でのリーダーシップを握るまでになり、これからはスーパーコンピュータ市場に「破壊的イノベーション」をもたらしていく意向を示した。

HPCの省電力のために“脱CPU”

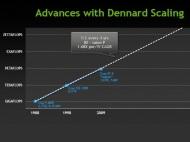

HPC開発では、半導体の微細化と性能向上に関して、IBMのロバート・デナード氏が提唱した「デナードのスケーリング則」にそって、CPUの高性能化を進めつつ、CPU搭載システムをクラスタリングすることで演算性能を引き上げる手法を続けている。この手法で常に絶対的性能を高めることを最優先してきた。

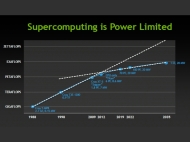

しかし、現在は一層の高性能化を図る一方で、省電力化も進める必要性に迫られている。そこで、ファン氏は、「HPCの開発においても、ノートPCやモバイルデバイスなどと同じく、フォームファクタや消費電力の許容範囲を早急に定義すべきだ」と主張する。その指標となるのが、UHPCプログラムが定める20メガワットの枠内だ。この枠の中で2019年には1エクサFLOPSの演算性能を実現すべきというものだ。

ファン氏は、HPCの高性能化のペースをCrayのスーパーコンピュータの進化を例に紹介。1998年までは、4年間で半導体の容量が半分になり、同期間に8倍のパフォーマンスアップを続けてきたことで、消費電力当たりの性能は年に1.68倍に成長し続ける順調な進化を遂げてきた。しかし、ここ数年はCPUの性能向上のペースが鈍化し、消費電力当たりの性能は年に1.19倍の成長にまで鈍化している。

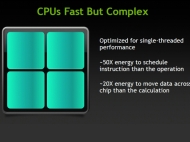

その理由をファン氏は「CPUは高速だが複雑すぎるため」だと説明する。現在のCPUは、シングルスレッドの性能を引き出すために最適化しており、演算処理に必要とされる消費電力の50倍もの電力を、演算処理の効率的なスケジューリングを行なうために使っている。さらに、HPCなど大量のデータを演算処理する用途では、データの“受け渡し”にかかる消費電力も、演算処理にかかる電力の20倍(これにはノード間のデータ通信も含まれると考えられる)に達する。

ファン氏は、2期連続で世界No.1の演算性能を維持した「京」が10ペタFLOPS(浮動小数点演算を毎秒1京回行える性能)を達成するために、12メガワットの電力を消費していることを指摘する。現段階で、1エクサFLOP(=1000ペタFLOPS:浮動小数点の演算を毎秒100京回行える性能)を実現するならば、「単純計算で約100倍弱の電力、原子力発電所2基分を必要とするだろう」と、20メガワットでエクサスケールの演算性能を実現する難しさを明らかにし、現在のCPUの高性能化ペースでは、「20メガワットで1エクサFLOPSの演算性能を実現するためには、2035年まで待たなければならない試算になる」と警告する。

2009年まで、HPC市場向けシステムは“デナードスケーリング則”にそって、半導体の微細化と性能向上によって演算処理性能を順調に高めてきたが、ここに消費電力の壁が立ちはだかった(写真=左)。CPUの消費電力を抑えるアプローチに変更した2010年以降、CPUベースのHPC性能向上のペースは大幅に鈍化、エクサスケールの実現には2035年までかかる公算に(写真=中央)。CPUは高速だが、シングルスレッド性能を高めるべく、演算処理以外の多くの電力消費を割いていると指摘(写真=右)

2009年まで、HPC市場向けシステムは“デナードスケーリング則”にそって、半導体の微細化と性能向上によって演算処理性能を順調に高めてきたが、ここに消費電力の壁が立ちはだかった(写真=左)。CPUの消費電力を抑えるアプローチに変更した2010年以降、CPUベースのHPC性能向上のペースは大幅に鈍化、エクサスケールの実現には2035年までかかる公算に(写真=中央)。CPUは高速だが、シングルスレッド性能を高めるべく、演算処理以外の多くの電力消費を割いていると指摘(写真=右)関連キーワード

GPU | HPC | NVIDIA | 電力 | イノベーション | 消費電力 | スーパーコンピュータ | スーパーコンピュータTop500 | GPUコンピューティング | 電力効率 | NVIDIA Tesla | CUDA | 技術開発

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- 「IBMはテクノロジーカンパニーだ」 日本IBMが5つの「価値共創領域」にこだわるワケ (2024年04月23日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- Googleが「Google for Education GIGA スクールパッケージ」を発表 GIGAスクール用Chromebookの「新規採用」と「継続」を両にらみ (2024年04月23日)

- バッファロー開発陣に聞く「Wi-Fi 7」にいち早く対応したメリット 決め手は異なる周波数を束ねる「MLO」【前編】 (2024年04月22日)

- ロジクール、“プロ仕様”をうたった60%レイアウト採用ワイヤレスゲーミングキーボード (2024年04月24日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- 「Surface Go」が“タフブック”みたいになる耐衝撃ケース サンワサプライから登場 (2024年04月24日)

- アドバンテック、第14世代Coreプロセッサを採用した産業向けシングルボードPC (2024年04月24日)